Basic Computer Components

Many OS textbooks (often in their 1st or 2nd chapters)

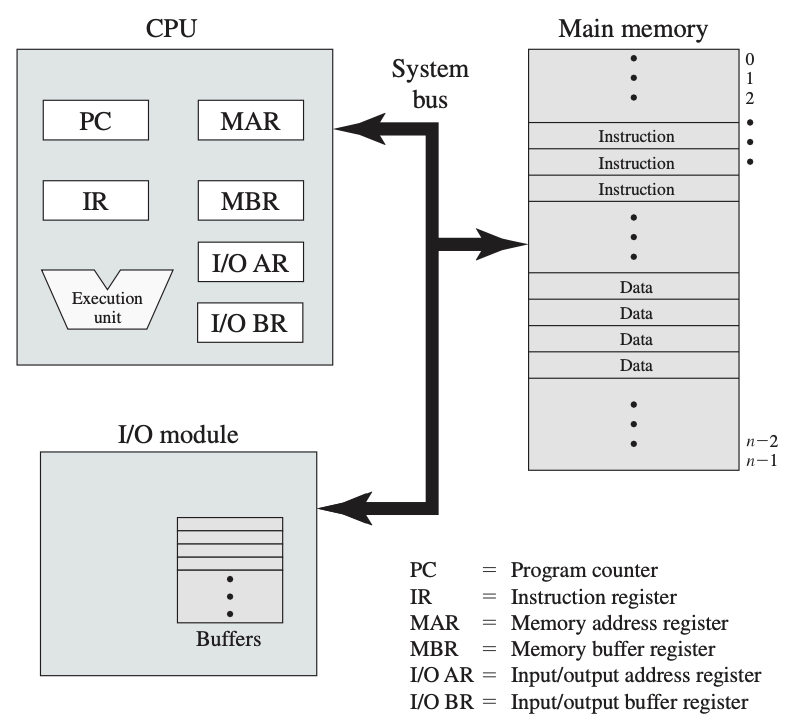

outline a traditional computer model, in which the

CPU, main memory, and I/O devices are all interconnected by a single system

bus

(figures are taken from

Stallings' website).

|

Instruction and data fetching

- The CPU fetches a copy of the contents of uniquely-addressed memory

locations, by identifying the required location in its

MAR (Memory Address Register).

- Depending on why the CPU requested the memory's value,

it executes the contents as an instruction,

or operates on the contents as data.

- Similarly, the CPU locates data from, or for,

distinct locations in the I/O devices using its I/O-AR (Address Register).

Role of operating systems

The role of the OS in managing the flow of data to and from its

CPU and I/O devices,

made very challenging by the wide variety of devices.

The OS attempts to attain maximum throughput of its

computation and data transfer.

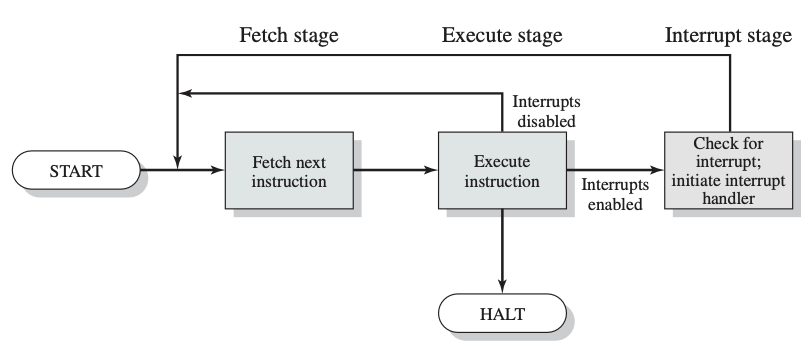

Processor scheduling attempts to keep the

(expensive) processor busy at all times,

by interleaving computation and communication.

While waiting for a slow device to complete its I/O transfer,

the CPU may be able to undertake other activities,

such as performing some computation or managing faster I/O.

|

CITS2002 Systems Programming, Lecture 6, p2, 7th August 2024.

|

CITS2002

CITS2002 CITS2002 schedule

CITS2002 schedule